本帖最后由 回忆往来 于 2021-7-13 12:38 编辑

什么是RS485总线rs-485采用半双工工作方式,支持多点数据通信。rs-485总线网络拓扑一般采用终端匹配的总线型结构。即采用一条总线将各个节点串接起来,不支持环形或星型网络。 rs-485采用平衡发送和差分接收,因此具有抑制共模干扰的能力。加上总线收发器具有高灵敏度,能检测低至200mv的电压,故传输信号能在千米以外得到恢复。 有些rs-485收发器修改输入阻抗以便允许将多达8倍以上的节点数连接到相同总线。rs-485最常见的应用是在工业环境下可编程逻辑控制器内部之间的通信。

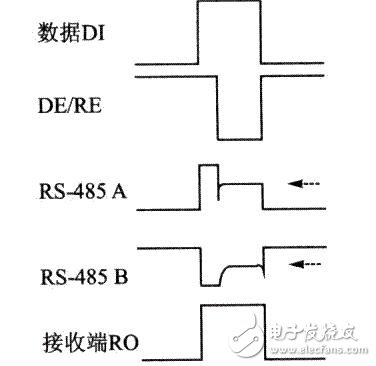

RS-485总线半双工延时问题 在半双工状态下 485 帧的收发和 总线的收发状态切换延时问题 对485总线长期稳定的工作有很大影响。彻底搞懂这个问题 对了解误码产生、数据丢失、总线的稳定性、可靠性都有重要意义。 1、每一帧收发停止位(或第9位)的延时问题 在RS-485半双工通讯中,一般以单片机的TI,RI信号作收发切换控制信号,发送时,检测TI是否建立起来,当TI为高电平后关闭发送功能转为接收功能,接收时,检测RI是否建立起来,当RI为高电平后,接收完毕,又可以转为发送。因此,必须控制端RE*,DE的信号的有效脉宽应该大于发送或接收一帧信号的宽度。

从上面的时序图可知:单片机在串行口发送数据时,只要将8位数据位传送完毕,TI标志即建立,但此时应发送的第九位数据位(若发送地址帧时)和停止位尚未发出。如果在这时关闭发送控制,势必造成发送帧数据不完整。 接收数据时也同样如此,单片机在接收完8个数据位后就建立起RI信号,但此时还未接收到第九位数据位(若接收地址帧时)和停止位。所以,接收端必须延时大于2位数据位的时间(1位数据位时间=1/波特率),再作应答,否则会发生总线冲突。 总之,发送和接收控制信号应该足够宽,以保证完整地接收一帧数据,任意两个单机的发送控制信号在时间上完全分开,避免总线争端。 注:延时T秒的取值 (1) 传送地址帧时,T》2X(1/波特率),可以选取T=2.5X(1/波特率)。 (2) 传送数据帧时,T》1X(1/波特率),可以选取T=1.5X(1/波特率)。 实际的软件流程:

可看到软件流程并没有在 每一帧收发停止位(或第9位)后实现延时,而是在(数据包的)最后一个字节(帧)上延时。这样能保障数据帧的正确(完整性)和稳定性吗? 2、半双工总线收发切换延时问题 为了可靠的工作,在485总线状态切换时需要做适当延时,再进行数据的收发。具体的做法是在数据发送状态下,先将控制端置“1”,延时1ms左右的时间,再发送有效的数据,一包数据发送结束后再延时1ms后,将控制端置“0”。这样的处理会使总线在状态切换时,有一个稳定的工作过程。 问题: 这里的 1ms是如何计算的? 485总线收、发状态切换时需要做适当延时,是指 485芯片的收发切换需要延时还是 485总线电缆固有的特性? :智能控制收发器(整理)

用内置微处理器实现收发使能的智能控制。 具体方法:微处理器在检测到UART的通信起始位后(低电平),打开发送使能,允许串行数据发送至RS-485/RS-422 通讯网络。微处理器根据所设定的波特率延时至UART停止位发送一半时,例如11位格式时,延时10.5T(T=1/fBAUD),然后开始检测是否有下一个起始位到来,在时间T内若有下一个起始位到来则保持发送状态。否则,将关闭发送使能结束数据发送,重新开始检测UART的起始位。 U3采用Microchip公司的 PIC12C508A,其中 GP0 GP1 GP4和GP5四个引脚设定对应于16 种常用波特率300 600 1200至38.4Kbps等8 种,以及900 1800 至 115.4Kbps等8种的延时时间。GP3对应于10位或11位串行数据格式,GP2为TXD输入用来检测UART何时发送和停止数据,GP1为复用输出引脚用来控制MAX3491的发送使能控制端,GP0也为复用输出引脚用来控制MAX3491的接收使能。 输出1时,485芯片不工作,总线仍然处于接收状态,靠上拉电阻保证差分电路输出1。

零延时电路图:

零延时电路波形图: 和上面电路比,输出1时,485芯片也有短时(RC延时)输出。  ] ]

他们如何保证 “控制端RE*,DE的信号的有效脉宽应该大于发送或接收一帧信号的宽度” 的? 这个已经理解了,这两个电路没有使用 单片机来切换,所以不存在发送最后一个帧需要延时的问题。 但是这个问题依然存在: 为了可靠的工作,在485总线状态切换时需要做适当延时,再进行数据的收发。 这两个电路在状态切换时都没有按这个要求来延时。 高手的艰难颠簸----Q118.RS-485总线的方向控制如何实现?要注意什么? 3 换向控制 总的来看,真正传输数据前先打开驱动器的条件不应改变,只有这样才能保证数据可靠地传输(按常规就是这样做的)。现在的问题是:打开驱动器的时间总是要占用时间的,要求还必须是低电平,高电平不起任何作用。同时,直接用数据打开驱动器是不可取的,这样做有损坏数据的危险。因此,可以这样说,设计思路上与使用I/O口先打开DE再发送数据的思路是一样的。为了达到不需要I/O干预,那么就需要使用专门的开启代码机制解决吧。 通过线与让I/O控制先送出开启电平来开启驱动器比之由数据线先送一个字节开启代码相对简单,虽然电路稍为复杂一些,但不对接收方识别提出要求。线与的方法优点是之一占用时间少又类似常规机制;第二个优点是节省光耦,即在线路采用光隔离措施时能与数据线共用一个光耦。但必须在发送真正的数据前及时退出。为了及时准确控制,感觉用单稳态触发器为好。图3的电路,影响时间常数的主要因素是数据速率。速率高,时间常数要小些,速率低,时间常数要大些。调试相对难是这个电路的不一定的不足。不过,要注意这个电路的两个时间常数并不相同,原因是C2要经过Q4的发射结放电,而C1不存在这样的问题。该电路的不足还有收发控制电平不是数字信号而是模拟信号。

文章摘自:解决rs485半双工总线延时问题解析 - 全文 - 接口/总线/驱动 - 电子发烧友网 (elecfans.com) 文本样式测试帖【】

|  发表于 2021-7-13 12:34:36

8038 浏览 0 回复

发表于 2021-7-13 12:34:36

8038 浏览 0 回复